сигнал для исполнительного механизма (двигателя).

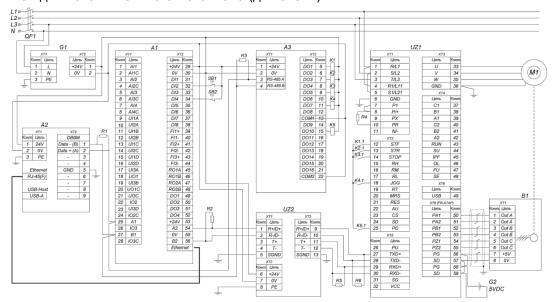

Рисунок 2 – Электрическая схема подключения установки элетропривода

Заключение. Лабораторная установка позволяет разрабатывать методы исследования деформационно-прочностных свойств выпускаемых изделий с использованием двухосного растяжения, оценивать технологичность и качество материалов обуви, оптимизировать режимы технологической обработки материалов при изготовлении обуви. Разработанную установку целесообразно применять в качестве испытательного оборудования на предприятиях обувной промышленности.

УДК 621.382:004.94

## МОДЕЛИРОВАНИЕ МЕМРИСТОРОВ С ИСПОЛЬЗОВАНИЕМ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ В СИМУЛЯТОРАХ ЭЛЕКТРОННЫХ СХЕМ

Черненко Д.В., ст. преп., Куксевич В.Ф., ст. преп., Астапенко Е.В., студ., Видунок Н.В., студ.

Витебский государственный технологический университет, г. Витебск, Республика Беларусь

<u>Реферат.</u> В статье рассмотрены теоретические основы работы мемристоров и результаты моделирования логического элемента И с использованием двух мемристоров.

Ключевые слова: мемристор, моделирование, логический элемент.

В последние годы внимание исследователей привлекают перспективные элементы, получившие название мемристоров, что обусловлено потребностью в энергонезависимой высокоскоростной памяти. Теоретически предсказанные Л. Чуа ещё в 1971 году, впервые элементы с требуемыми характеристиками получены сравнительно недавно на основе тонких пленок TiO2. Элементы памяти на основе мемристоров приближаются по своим характеристикам к получившей широкое распространение флэш-памяти и имеют перспективы в связи с рядом преимуществ.

Мемристор представляет собой пассивный нелинейный элемент электрической цепи и является фундаментальным наравне с резистором, конденсатором и катушкой индуктивности. Его нельзя получить комбинацией этих трёх хорошо известных базовых элементов классической теории электрических цепей. В отличие от обычного нелинейного

УО «ВГТУ», 2021 37

резистора, сопротивление мемристора зависит не от приложенного к нему в данный момент времени напряжения, а от напряжений (или токов) во все предыдущие моменты времени.

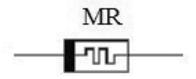

Условное обозначение мемристора представлено на рисунке 1.

Рисунок 1 – Условное обозначение мемристора

Сопротивление (проводимость) мемристора определяется его внутренним состоянием – распределением концентрации ионов в прослойке. В простейшем случае состояние описывается одной переменной, например, положением границы раздела между проводящей и непроводящей частью прослойки. Если состояние мемристора изменяется при протекании тока, то имеем мемристор, управляемый током; если под действием приложенного к нему напряжения, то имеем мемристор, управляемый напряжением.

На основе мемристоров могут быть созданы энергонезависимые запоминающие устройства, системы программируемой логики, нейронные сети, самонастраивающиеся аналогово-цифровые устройства управления.

В широком спектре научно-технических работ по мемристорам заметное место занимают вопросы их моделирования. Предложено большое количество моделей мемристоров. Они сводятся к конкретизации функций, чтобы соответствовать реальным (экспериментальным) данным. В частности, использование мемристоров для выполнения логических операций может осуществляться различными способами, например, применением их в качестве реконфигурируемых переключателей.

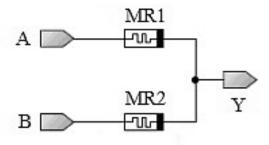

Так логическая функция И с использованием двух мемристоров MR1 и MR2 может быть реализована в соответствии с рисунком 2 [1].

Рисунок 2 – Логический элемент И на двух мемристорах

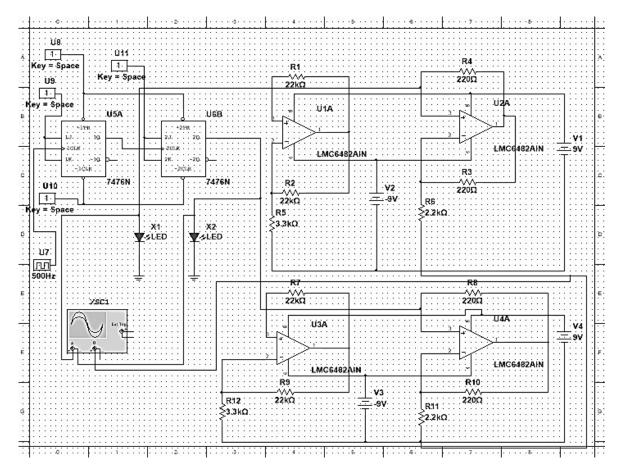

Реализация двухвходового логического элемента И на мемристорах была осуществлена в программе моделирования электрических цепей NI Multisim (рис. 3). При этом каждый мемристор реализован в виде схемы из двух операционных усилителей, а двухбитовый счетчик используется для генерации всех четырех возможных комбинаций входных сигналов.

Работа такого логического элемента осуществляется следующим образом. Когда вход A = 1 и вход B = 1, т.е. оба входа подключены, например, к источнику с напряжением 5 B, оба мемристора имеют одинаковый потенциал и, следовательно, ток через мемристоры не течет, а выход схемы будет иметь высокий уровень напряжения, т.е. Y = 1.

Когда вход A = 0 и вход B = 0, ток через мемристоры по-прежнему не течет, но теперь вследствие отсутствия разности потенциалов, выход Y = 0.

Рисунок 3 – Реализация логического элемента И в программе NI Multisim

Когда вход A = 1, а вход B = 0, сопротивление MR1 увеличивается до уровня Roff, в то время как сопротивление MR2 снижается до уровня Ron. Состояние выхода схемы при этом определяется правилом делителя напряжения:

$$Y = \frac{U \times R_{on}}{R_{on} + R_{off}}.$$

(1)

Поскольку, Ron << Roff, то Y = 0.

Когда вход A = 0 и вход B = 1, сопротивление MR2 увеличивается до уровня Roff, в то время как сопротивление MR1 снижается до уровня Ron. При этом согласно (1) состояние выхода схемы также будет Y = 0.

Полученные в результате моделирования результаты полностью согласуются с теоретическими положениями.

## Список использованных источников

NI Multisim and Experimental Validation Implitation of Ratioed Logic Gates Using Memristor [Electronic resource]. – Mode of access: http://journals.du.ac.in/ugresearch/DU%20e-Journal%20-%20UG%20Research\_files/DUJ4%20Vol%202%20Issue1/J%201.15.pdf. – Date of access: 14.05.2021.

УО «ВГТУ», 2021 **39**